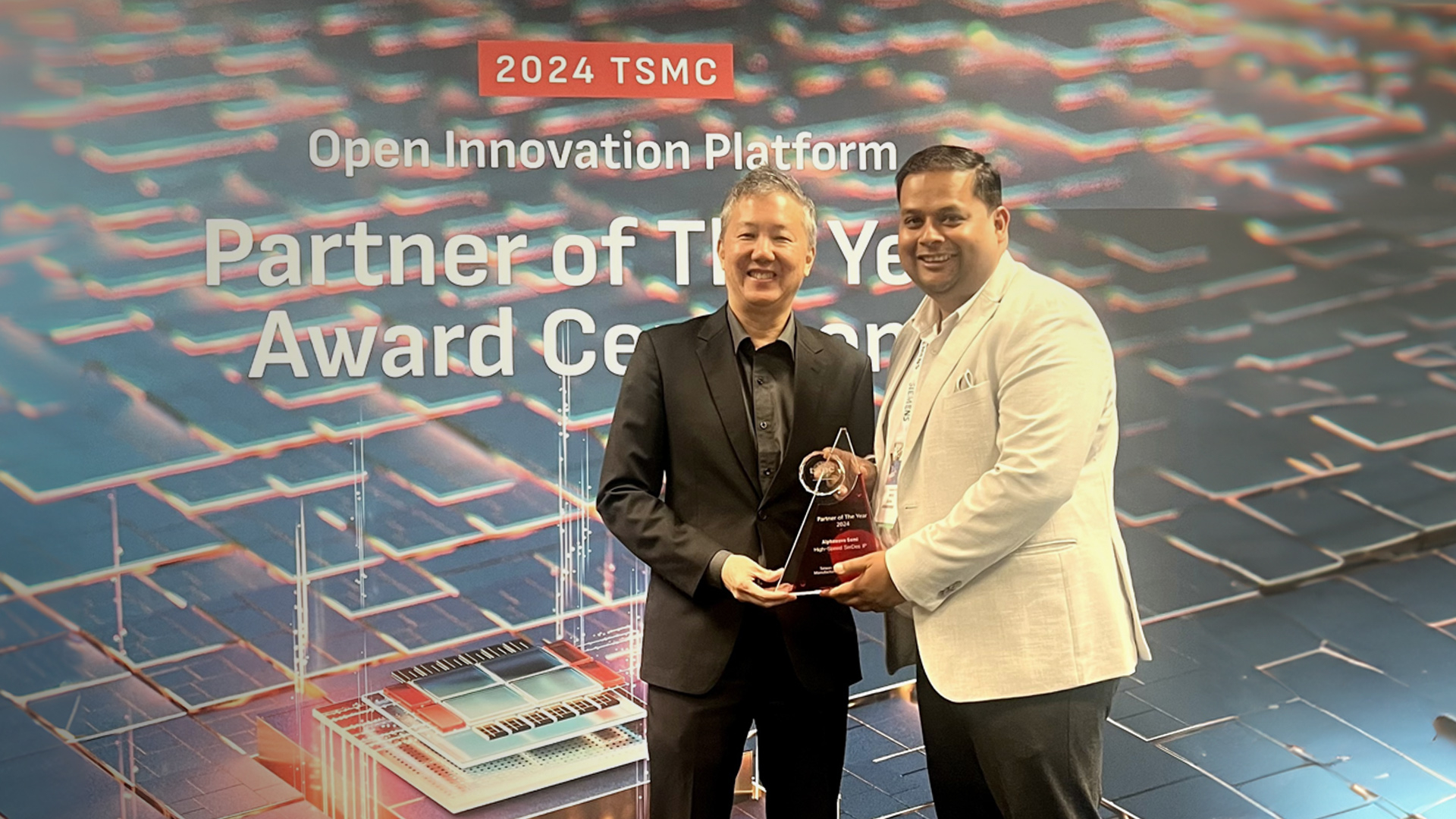

Alphawave Semi announced its recognition as the recipient of the TSMC 2024 OIP Partner of the Year Award for High-Speed SerDes IP.

This prestigious award marks the fifth consecutive year Alphawave Semi has been honored for its outstanding contributions to next-generation design enablement within TSMC’s Open Innovation Platform (OIP) ecosystem.

At the TSMC OIP Ecosystem Forum, Alphawave Semi was recognized for its advancements in silicon connectivity, notably for its multi-standard SerDes covering complete IP solutions up to 224Gbps, including Ethernet and PCIe on the most advanced processes, as well as its ZeusCORE100® 1-112Gbps NRZ/PAM4 SerDes on TSMC’s advanced N3E process. The event brought together semiconductor design partners and TSMC customers to explore advanced technologies across HPC, mobile, automotive, and IoT applications.

“Our collaboration with TSMC over the past year has resulted in significant breakthroughs, including the successful deployment of our first test chip on TSMC’s N3P process,” said Tony Pialis, CEO and co-founder of Alphawave Semi. “This partnership continues to drive the development of advanced connectivity solutions for networking, servers, and storage, meeting the demands of hyperscalers and semiconductor customers alike.”

Dan Kochpatcharin, head of the Ecosystem and Alliance Management Division at TSMC, added, “TSMC and Alphawave Semi are driving innovation to equip engineering teams with cutting-edge solutions for developing complex designs on advanced process nodes. These partner awards highlight the invaluable contributions from OIP ecosystem partners like Alphawave Semi, enabling the next generation of high-performance designs on TSMC’s technologies with significantly enhanced efficiency and accelerated time to market.”

Key Highlights from Alphawave Semi’s Participation:

- Groundbreaking Presentation: Alphawave Semi’s VP of IP Product Marketing, Letizia Giuliano, along with Arm’s Sridhar Valluru, delivered an insightful presentation titled “Architecting Next-Generation Terabit AI Networks with The Industry’s First Multi-Protocol I/O Connectivity Chiplet”. They explored the challenges of scaling AI and the pivotal role of UCIe-enabled AI chiplets in overcoming limitations in leading-edge SoCs.

- Industry Firsts: Alphawave Semi showcased several breakthrough innovations, including the industry’s first-ever 3nm UCIe IP with TSMC CoWoS packaging and the successful tape out of the first multi-protocol I/O connectivity chiplet designed for AI infrastructure.

- Live Demonstration: Attendees witnessed Alphawave Semi’s UCIe chiplet in action, demonstrating 24 Gbps per lane die-to-die communication, setting a new benchmark for high-performance computing.

- AI and HPC Technologies: The company also exhibited its HBM3E subsystem for AI workloads and its 128G PCIe 7.0 over optics IP, reflecting its commitment to addressing the growing needs of AI and HPC systems.