Macro-to-micro viewing capabilities of digital microscopes can help overcome common challenges in the inspection process.

Challenges to Replacing Hard-Disk Drives

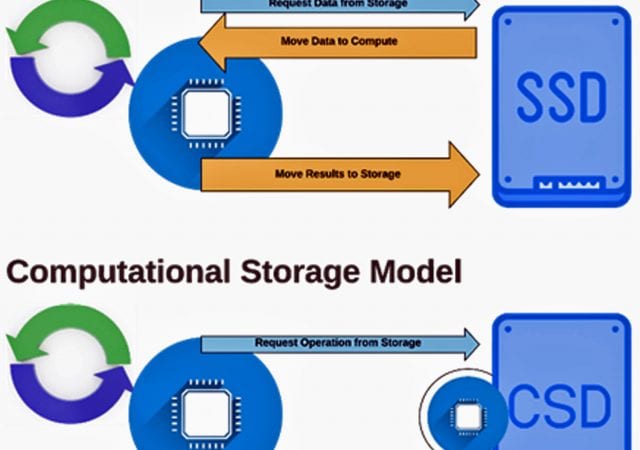

Computational storage devices are the new must-have peripherals for intensive storage applications.

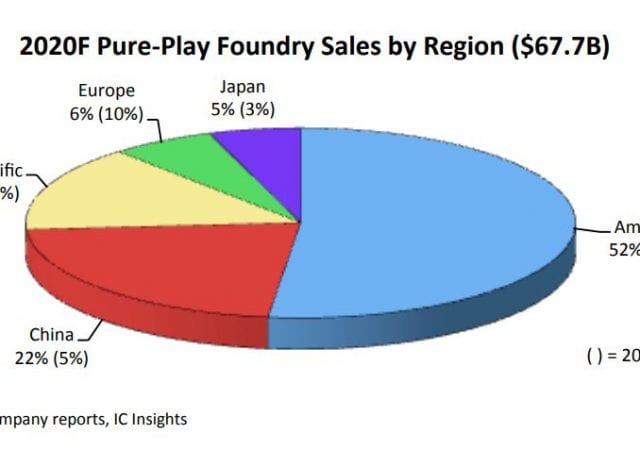

China Forecast to Represent 22% of the Foundry Market in 2020

Despite the Covid-19 shutdown of China’s economy earlier this year, China’s share of the pure-play foundry market is forecast to be 22% in 2020, 17 percentage points greater than it registered in 2010

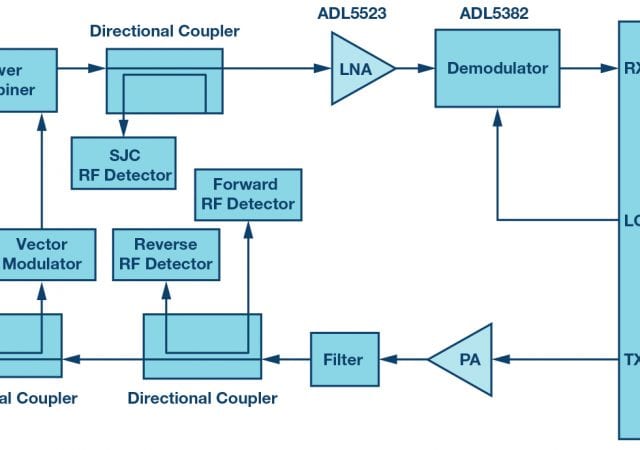

Developing a UHF RFID Reader RF Front End

Two implementations showing how engineers can trade off receiver sensitivity for reduced design complexity, component count, and board space in UHF RFID applications.

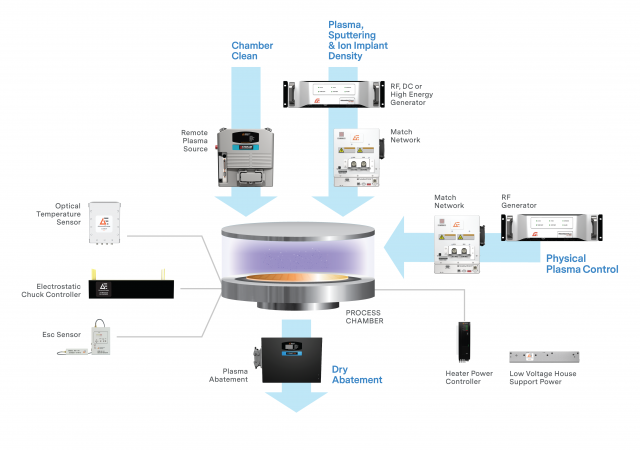

Powering Ahead

Integrated RF and tuning networks, solid-state tuning networks, non-sinusoidal bias for tailored ion energy distribution, and predictive power delivery will enable process applications at advanced technology nodes.

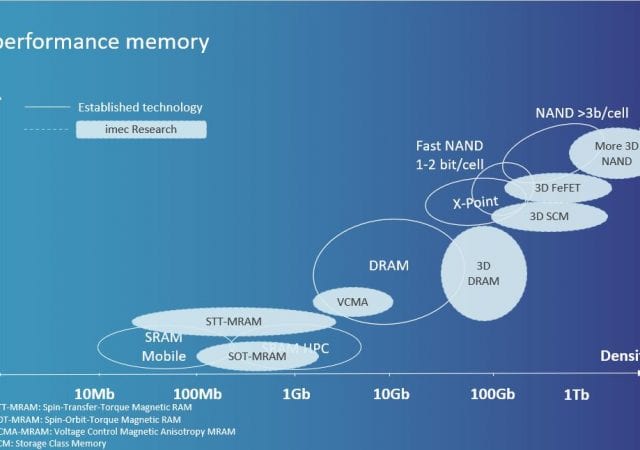

Five Trends That Will Shape the Future Semiconductor Technology Landscape

Is Moore’s Law still alive, and which applications will benefit from ultra-scaled technologies? How will data centers cope with the overwhelming amount of data? And will we be able to break the memory wall in traditional Von Neumann computing architectures?

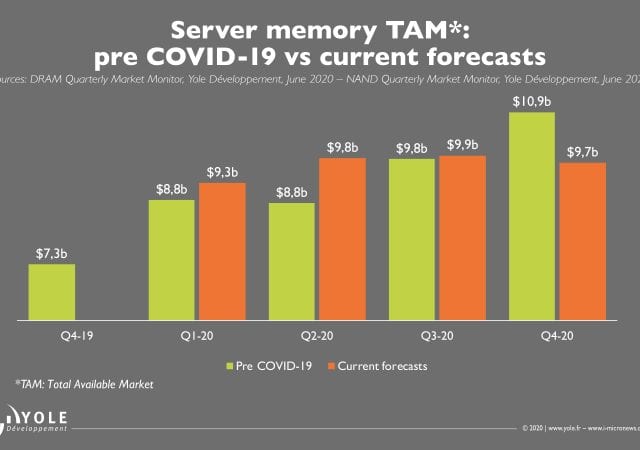

How COVID-19 is Impacting the Memory Industry

Heading into 2020 both the DRAM and NAND industries were projected to have turn-around years after suffering through much of 2018 and 2019. However, with the global lockdown triggered by the COVID-19 pandemic the outlook for the industry has changed considerably, and not all the change is for the worse. In this article we explore the impact on memory demand, how suppliers are expected to react to the pandemic, and the likely impact to pricing over the near-to-midterm.

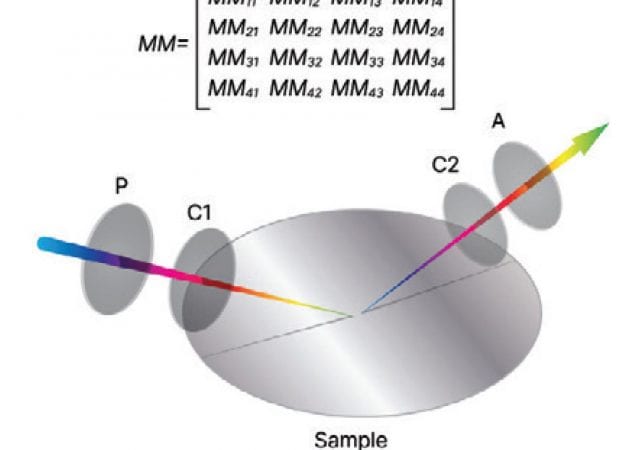

Metrology Solutions for Gate-All-Around Transistors in High Volume Manufacturing

High-speed, non-destructive OCD metrology has the capability needed to support process control throughout the GAA process flow.

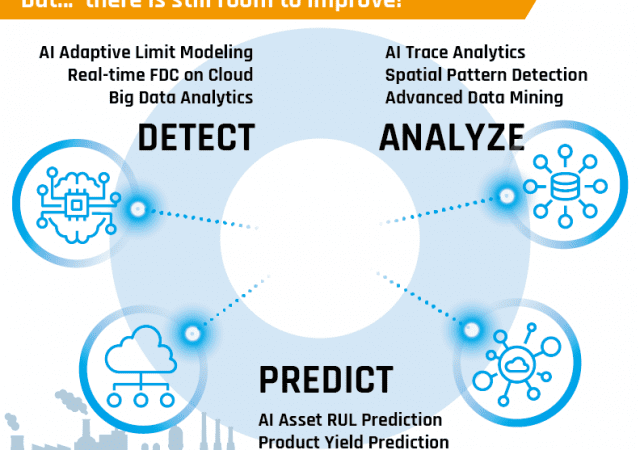

Fab Models Built on AI Collaborative Knowledge Sharing

New AI knowledge sharing fab models will play a leading role in shaping the fab of the future.

Onto Innovation: A Mid-Year Update

Onto Innovation (ONTO), created last year by a merger of Rudolph and Nanometrics, focuses primarily on optical metrology, macro defect inspection, process control software, and panel lithography.