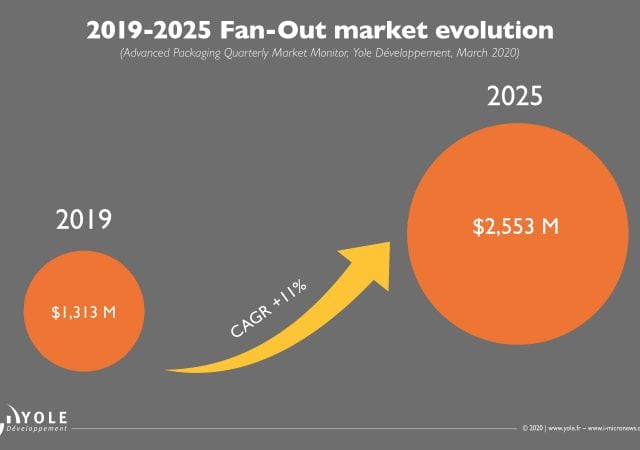

Fan-out package revenue is expected to surpass $2B by 2025 and fan-in WLCSP revenue to peak to $3B by 2025 as TSMC continues to drive the fan-out market in 5G applications.

Intel Replaces 10+ with Tweaked SuperFin Technology

Intel held their virtual 2020 Architecture Day on August 13th, hosted by Raja Koduri, and the first major topic was Process Innovations, with Ruth Brain as the presenter. Ruth started with a potted history of Intel processing, from the first strained channel at the 90-nm node to the string of 14-nm evolutions.

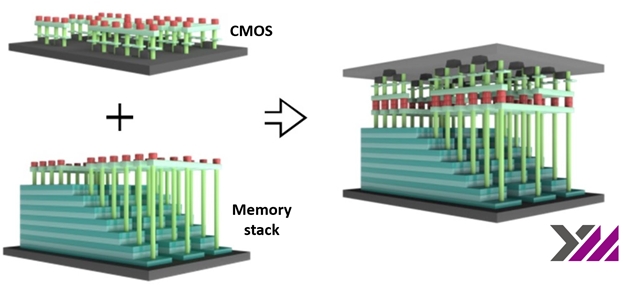

Unlocking the Secrets of the YMTC 64-Layer 3D Xtacking® NAND Flash

A look inside YMTC’s second-generation 3D-NAND technology, which uses “Xtacking” to bond the peripheral circuitry face-to-face with the memory array instead of alongside.

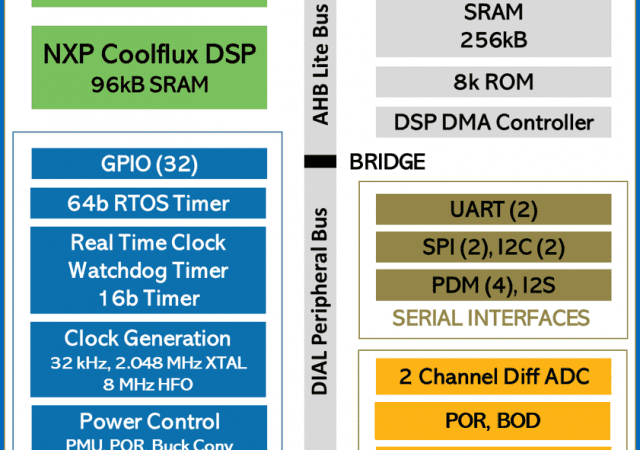

Yes, We CAN Preserve Personal Privacy in Voice-First Consumer Devices

A better balance between cloud and edge processing is a better balance between convenience and privacy, and that’s a win for everyone.

Epitaxy: An Epic Growth

Epitaxy growth equipment for More than Moore devices technology.

VLSI Design Optimization and Validation Process Is Like Painting the Forth Bridge

Some EDA tools have introduced an innovative approach that allows designers to generate design metadata one time for certain verification flows.

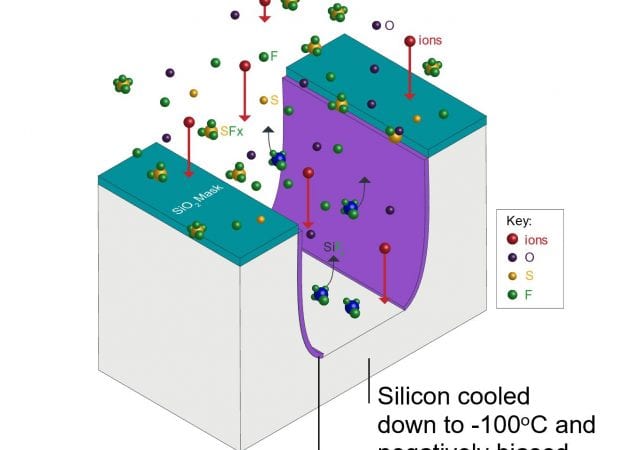

Understanding Cooling and Particulate Contamination Challenges for Next Generation ALE Technologies

Mixed-refrigerant Joule-Thomson refrigeration can provide the necessary wafer temperatures and cooling power with smaller footprint, better reliability and lower power consumption than alternative cooling technologies. Cryo-trapping can reduce particle generation by removing the water that mediates the particle formation process.

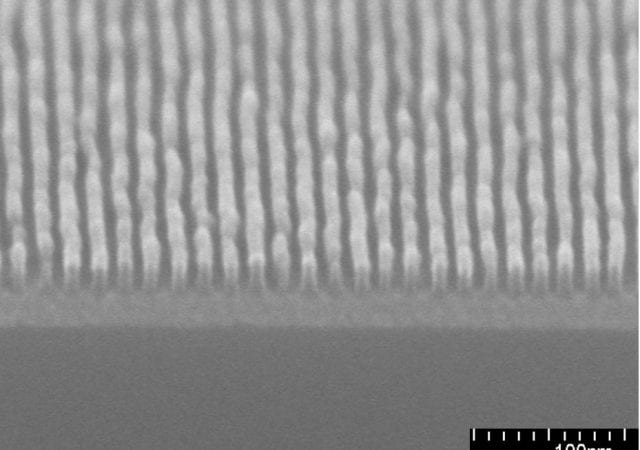

Building Patterns From The Bottom: A Complementary Approach to Lithography

With shrinking dimensions, the classical lithography-based top-down patterning processes are becoming extremely complex and expensive. Therefore, researchers worldwide are investigating alternative processes allowing to build patterns from the bottom. Two promising approaches are directed self-assembly (DSA) and area-selective deposition (ASD).

Deep Learning at the Extreme Edge: A Manifesto

With continuous voltage and frequency scaling, the logic is self-timed, adjusting core voltage and clock frequency automatically, ensuring no timing violation. This allows the chip to always run the most efficient way for a given workload.

The Chip Wars Get Real

There was a lot of big news in the semiconductor industry during the last week as the U.S., China and Taiwan face off in a chip war over Huawei.