John Blyler, Senior Contributing Editor, Semiconductor Digest

Any query that asks for the latest trends in the EDA-IP chip design space will come up with four common topic areas: 3D ICs, AI, quantum, and supply chains. But all these subjects have been in the limelight for several years. What is new in 2023? To find out, Semiconductor Digest asked experts from the EDA-IP, systems, and standards spaces (respectively): Joe Sawicki, Executive Vice President, Siemens IC EDA; Manuel Rei, Semiconductor Solution Experience Director at Dassault Systèmes; Lu Dai, Accellera Standards Chair. The following is an edited version of their responses. – John Blyler

Semiconductor Digest: How are recent changes in the global chip and board design-manufacturing processes (including the CHIP Act) impacting the EDA-IP industries?

Lu Dai: We expect changes to come out of the CHIPS Act, but we don’t know their overall effects as many countries have their own version. There could be some curtailing of open-source development and maybe tighter export control on open-source development with CHIPS Act funding. However, traditional EDA companies with their in-house design may actually benefit in this new environment, even though it may not be good for overall technology development.

Manuel Rei: The most important change will be how we work together, such as collaboration across various alliances and consortiums. These changes are important as they affect the speed of innovation and visibility on the supply chain and sovereignty.

The US, Europe, and India are poised to gain market share thanks to new investments on the manufacturing side. However, while EDA design comes mainly from US companies, domain, and flow-specific AI-based applications may potentially disrupt existing market players.

Semiconductor Digest: How will ongoing improvement in 3D-IC (like chiplet) technologies affect Moore’s Law?

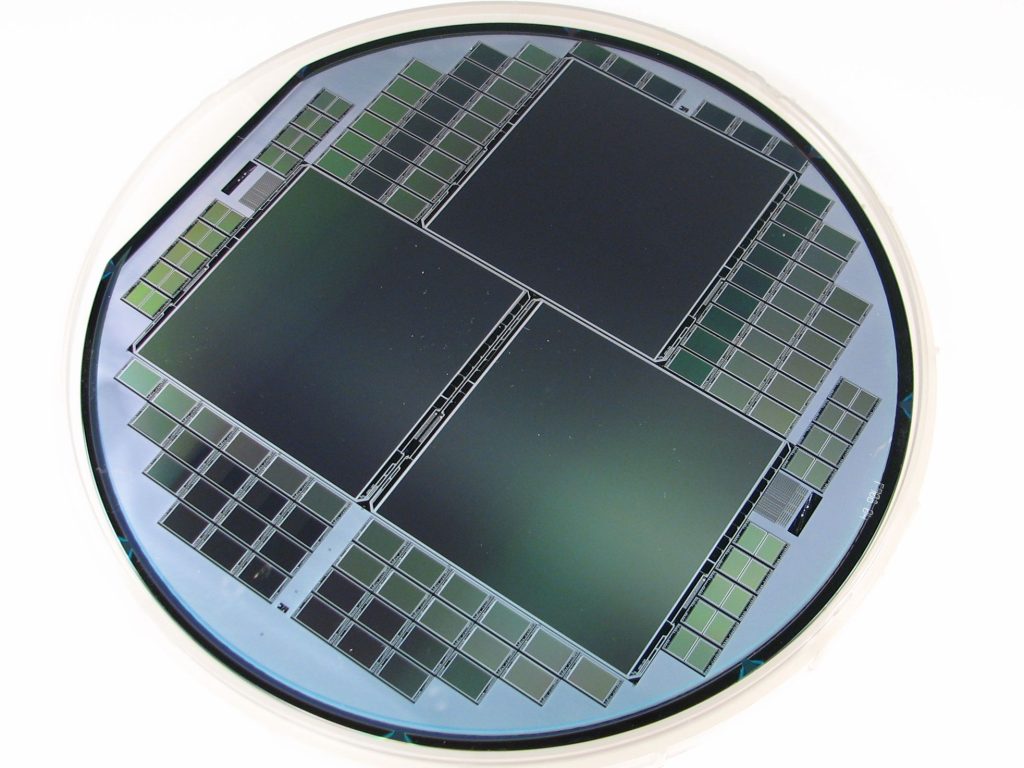

Joe Sawicki: At an IC level, it can enable chip companies to develop smaller dies while yielding more known good dies per wafer, as a smaller percentage will be adversely affected by random defects. And at the system level, 3D IC enables companies to achieve new levels of miniaturization and reduce BOM costs. But, far more importantly, 3D IC enables design teams to place or stack different types of ICs – SoCs, analog ICs, and memory ICs (each implemented in their ideal process nodes) to achieve greater levels of system performance and functionality than is possible in conventional PCB or even SoC configurations.

As 3D IC becomes more mainstream, there’s industry-wide momentum to create a new industry standard for “chiplets” – small ICs that can be easily plugged into standard interposers for 2.5D IC design, or on top of one another in 3D configurations (think silicon LEGOs). Standards bodies like UCIe were established in 2022 to develop an ecosystem that will hopefully turn the plug-and-play capabilities of chiplets into a reality. EDA companies must be active in these efforts to ensure IC tool suites facilitate the creation of standards-compliant, socket-ready chiplets and that their larger 3D IC solutions do, too.

Manuel Rei: 3D integration will allow more performance (higher interconnection density, computing performance), miniaturization, and heterogeneous functionalities. These innovations will require extremely complex modeling and simulation applications to create device virtual twins, enabling designers to explore more and scale innovation from lab to fab more quickly.

Lu Dai, Accellera Chair: There has been a lot of discussion about chiplets. There must be a distinction between IP for chiplets and chiplets as a methodology to address design complexity. The latter has a more immediate need and is where the EDA industry should place a greater focus.

Semiconductor Digest: How are the growth of AI chips and quantum computing technologies affecting the EDA-IP industry?

Joe Sawicki: Whether it be system-level applications like autonomous driving, 5G networks, or chip-to-city type initiatives, knowing in advance how the system will perform (versus expectations) in the real world provides greater degrees of differentiation. The two biggest impediments to the IC industry in enabling full autonomous driving are power consumption and determining how much processing will be required as the system moves through a complex, real-world environment. AI has the potential to greatly help with the design and ecosystem complexities of such applications.

Manuel Rei: In a world where connectivity is everywhere, we see the growth of IoT, data usage, and the need for edge computing. Nevertheless, power consumption reduction is key and must be faster than the power needed for the new product. The next generation is thinking about processing on the IoT.

Quantum technology can allow computing performance, but AI will make the product and sensor intelligent. Depending on the usage, we will always optimize this usage to find the right compromise between performance, energy consumption, and latency.

Lu Dai: AI is a rapidly growing trend demanding very low power because of the massive amount of computation required. Much larger server farms are also needed. Another trend is in quantum computing. It presents an urgent need to upgrade security algorithms.

Semiconductor Digest: How will the evolution of open-source IP and software change the industry?

Manuel Rei: Open-source IP and software will remain a low market in semiconductor design as long as IP and software qualification and traceability are unclear. The reason to use more open-source IP and software is lower cost, but the legal and commercial binding behind private IP usage will prevail for most commercial designs. Also, innovation and differentiation always come with a premium, and those who have the power to pay more will likely be able to get a return on their investment.

Lu Dai: The industry has widely accepted open-source software. Open-source IP is a more recent development. It remains to be seen whether open-source IP will succeed similarly to its software counterpart, especially in the new CHIPS Act landscape. While it improves IP quality, the biggest benefit of open-source IP is enabling smaller/newer companies to compete with established bellwethers, in this case, newcomers from China.

Semiconductor Digest: What lies ahead for EDA tools considering growing export restrictions?

Manuel Rei: AI will revolutionize EDA automation, requiring export restrictions based on geopolitical options, as the same advanced node equipment makers have today. This will push non-US EDA companies to explore alternative design solutions. It is usually when you have no other choice but to survive that the most ingenuous solutions arise.

Lastly, due to the complexity of the product development chain (systems of systems of systems) and the need for the final product OEM to master their product innovation and differentiation, the design, integration, and management of semiconductor IP will require key software applications sharing the same ecosystem (design platform) to enhance and speed up collaboration throughout the entire value chain.

Lu Dai: Security is an increasingly important subject given the amount of data in the cloud, concerns about supply chain traceability, and the advancement in quantum computing. Newer algorithms are needed. Traceability could become mandatory. But we need to watch out to ensure overhead is not overbearing, especially when different national authorities require different solutions.

Semiconductor Digest: Thank you.

Cover Image Source: Windell Oskay, Creative Commons