In an article published in the most recent issue of imec’s online magazine (http://magazine.imec.be/) titled “Chips must learn how to feel pain and how to cure themselves,” researchers Francky Chatthoor and Guido Groeseneken discuss how to build reliable “5nm-node” ICs out of inherently unreliable transistors. Variability in “zero time” and “over time” performance of individual transistors cannot be controlled below the “7nm-node” using traditional guard-banding in IC design.

“Maybe it means the end of the guard-band approach, but certainly not the end of scaling,” says Groeseneken in the article. “In our research group we measure and tried to understand reliability issues in scaled devices. In the 40nm technology, it is still possible to cope with the reliability issues of the devices and make a good system. But at 7nm, the unreliability of the devices risks to affect the whole system. And conventional design techniques can’t stop this from happening. New design paradigms are therefore urgently needed.” These researchers predict that industry will have to manufacture self-healing chips by the year 2025.

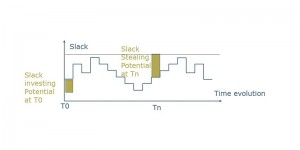

The ultimate goal of imec and its academic partners is to develop a fully proactive parametric reliability mitigation technique with distributed monitors, a control system and actuators, fully preventing the consequence of delay faults and potentially also of functional faults. Said Catthour, “the secret to the solution lies in the work load variation of the system. Based on a deterministic predictor of the future, you determine future slack and use this to compensate for the delay error at peak load. Based on this info on the future, you change the scheduling order and the assignment of operations.” The Figure shows how self-healing chips can use future slack to compensate for delay error and mitigate at peak load.

—E.K.