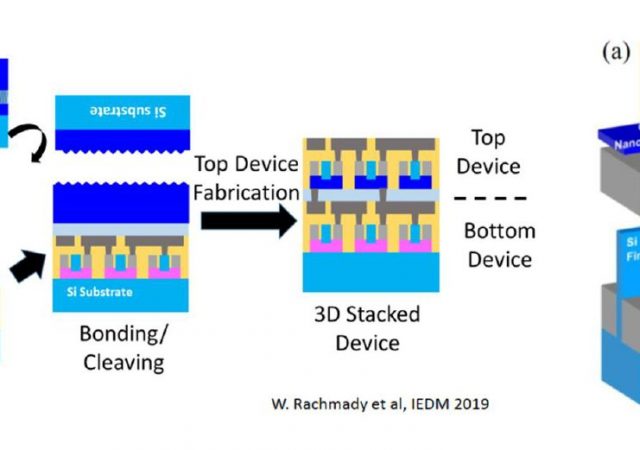

Chip design simulation remains an important tool, but manufacturing and supply chain simulators are equally critical – e.g., digital twins and chiplets. Die hardware integration security looks to be the new threat target for modern systems, and CMOS 2.0 may make the challenge even more significant.

Scaling Progress Takes Many Paths at VLSI Symposium

The IEEE 2022 Symposium on VLSI Technology and Circuits attracted 650 people to attend in person in Honolulu, and an equal number of virtual attendees.

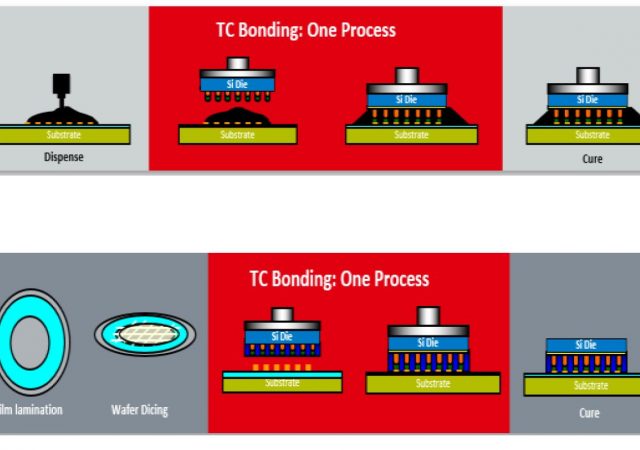

Maximizing Protection of Flip Chip Interconnects

NCP and NCF property and process optimization deliver high-reliability results.