By Dick James, Senior Technology Analyst, Chipworks

For us at Chipworks interested in leading edge processes, 2014 so far has been the year of waiting for parts and processes that have been announced, but not shown up in the world of commercial production. It will surprise no-one in the business that they are Intel’s 14-nm, the 20-nm products from any of the big three foundries (in particular TSMC), and vertical NAND (in particular Samsung, since they are the first claiming shipment).

There are of course other products that we are anticipating such as the latest SDRAM, STT or resistive RAM, and anything with TSVs, but they are lower-key and will not get the same attention from the majority of our customers.

So now the first shoe has dropped (must check where that metaphor came from!), and we have a TSMC-fabbed 20-nm part in-house. It is in the lab at the moment, and we are waiting for the analysis results.

It will be interesting to see what changes TSMC has made from the 28-nm process; in general, I expect mostly a shrink of the latter process, with no change to the materials of the high-k stack, though maybe to the sequence. At 28-nm the high- k was put down first, before the dummy poly gate, and it makes sense to move that deposition to after poly gate removal. That way, the high-k layer does not have to suffer the poly formation and source-drain engineering process steps, saving it from quite a bit of thermal processing.

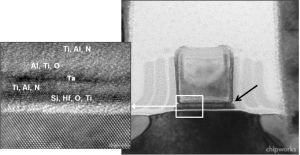

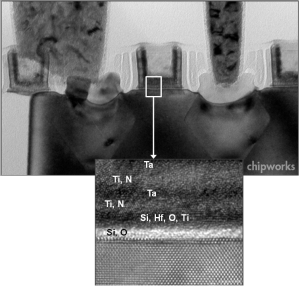

Below is an illustration of a NMOS transistor from a Qualcomm Snapdragon 800, fabricated in the TSMC 28HPM process. The slight indent at the bottom of the metal stack (indicated by the arrow), above the high-k layers, indicates that the high-k was formed before the polysilicon deposition and the subsequent source/drain engineering.

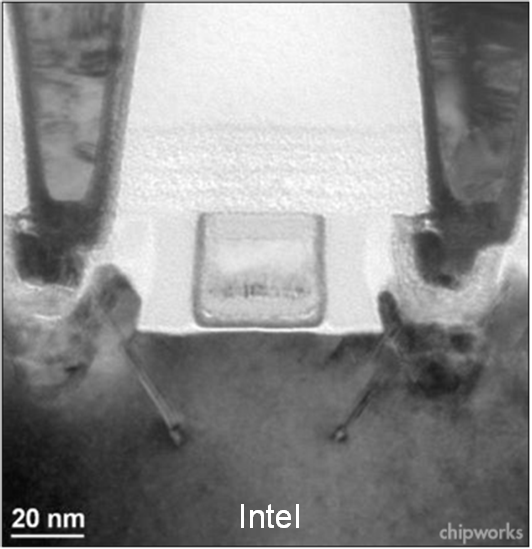

The dark line at the perimeter of the metal gate is the tantalum-based barrier layer between the Ti-Al work-function doping layer and the TiAlN work-function layer, and is the first layer formed after the dummy poly removal. Intel used this sequence for their 45-nm process, but modified it at the 32-nm node to deposit the high-k stack after poly removal (high-k last – see below).

You can see that Intel also adopted raised source/drains, with stacking faults to apply tensile stress; we will see if TSMC does the same in their second generation gate-last HKMG process. They could also change the gate fill metal, since in a smaller gate it may be difficult to use the PVD Ti/Al/Cu from the 28nm sequence.

As for the back-end, presumably there will be a reduction in the k-value of the low-k dielectric, and maybe some thinning of the barrier layer in the metal trenches, both of which are trends that progress relatively slowly by comparison with the front-end.

Back in May, Applied Materials announced a cobalt CVD system aimed at improving copper fill and electro-migration performance. I wouldn’t have expected to see this in use yet, but at Semicon I heard that over 90 of these systems have already been shipped, so there is at least a possibility that we’ll see cobalt in our 20-nm metallization.

All pure speculation, but as a blogger and analyst, I’m paid to speculate!

As for “the first shoe drop”, it’s a variant on “waiting for the other shoe to drop“; apparently it’s a reference to cheap apartment housing where tenants would hear their neighbours above taking off and dropping their first shoes on to the floor; and then wait for the second shoes to drop.