Mark Liu, Chairman of Taiwan Semiconductor Manufacturing Company (TSMC), provided detailed insights into the company’s technology roadmap at the recent International Solid-State Circuits Conference (ISSCC), held virtually Feb. 13-22. He said the semiconductor industry will need to adopt methods to measure system-level benefits in addition to traditional transistor-level or chip-level methods. As semiconductor technologies continue to advance with better transistors, advanced memories, more efficient signals and power delivery, new materials, DTCO, and 3D structures, greater value will be delivered to the user when these advances are combined with intelligent system partitioning into domain-specific technologies, chiplet integration, and advanced packaging technologies.

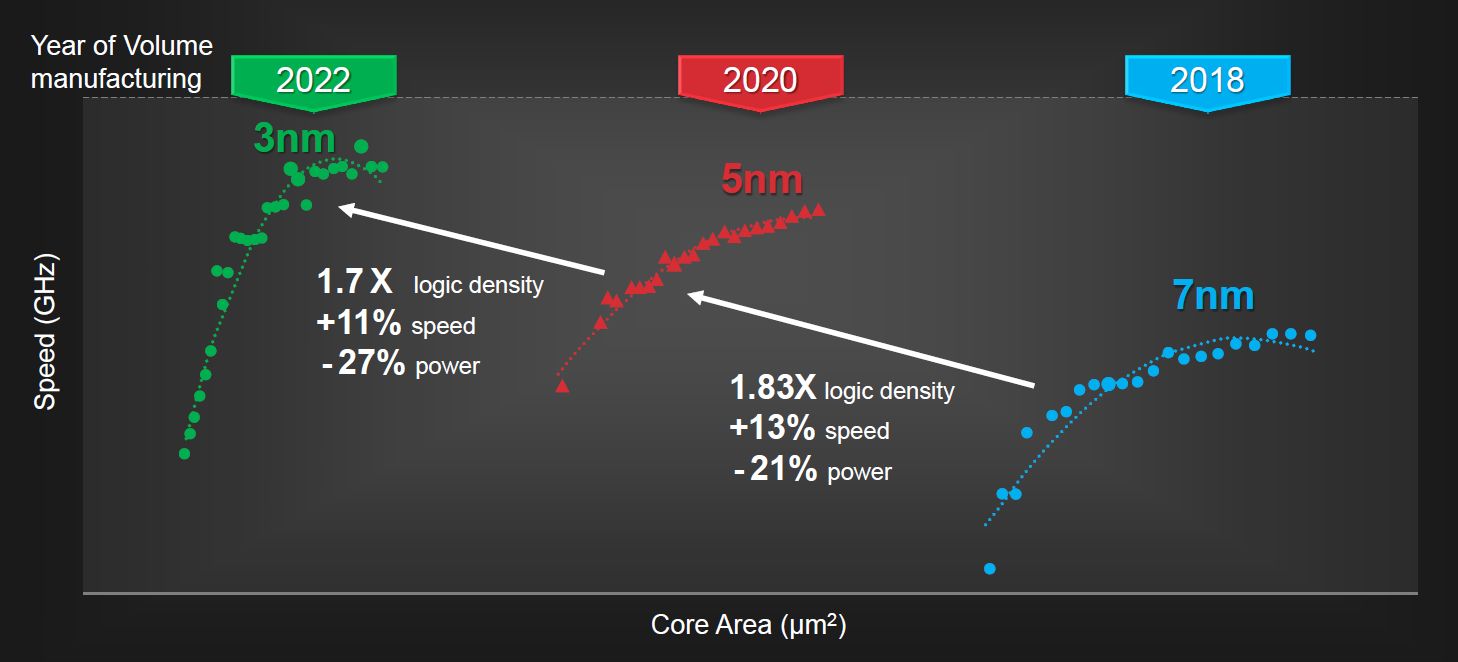

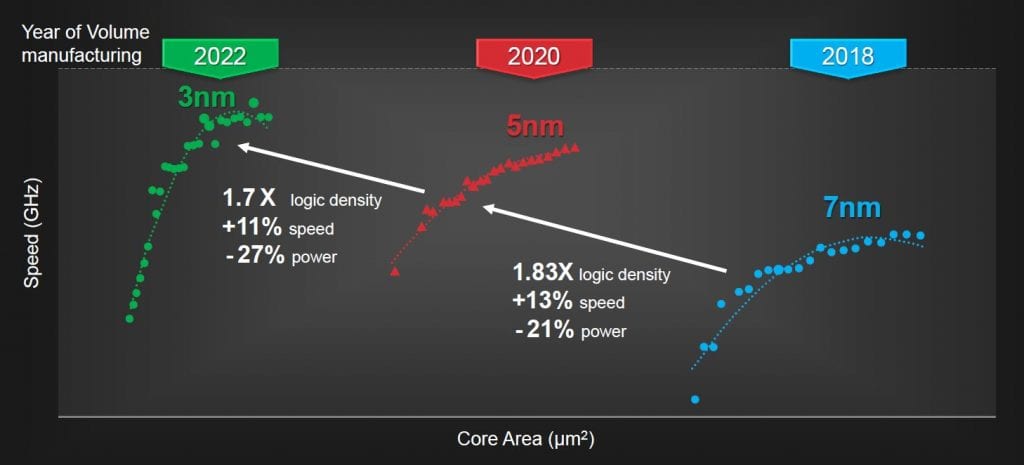

Liu waved off the suggestion that device technology improvements are slowing down. “Our product data shows a power reduction at the same speed or speed gain and the same power and logic density are still right on track to sustain the historical trend over the past five generations with 5nm being a full scale node and 3nm being another full scale node.” He said 3nm technology development is making good progress and well on schedule. “Looking ahead, industry and academia have been working closely to innovate in new transistor structures and new materials along with new system architecture and 3D integration to sustain the technology advancement beyond 3nm,” he said.

In the March issue of Semiconductor Digest, Editor-in-Chief Pete Singer summarizes Liu’s talk. Click here to read the full article.