John Blyler, Contributing Senior Editor, Semiconductor Digest

The recent CHIPS Act boosted support of semiconductor R&D, manufacturing, and workforce development within the US. While the act paid little attention to the semiconductor intellectual property (IP) market, the message was implicit since, without IP, the chip industry would not exist as we know it.

Modern chip development within a fabless business model requires a robust, integrated IP ecosystem. For this reason, IP has long been a significant growth area for the electronic design automation (EDA) tools market, where much of the revenue in the EDA software tool chip design space comes from IP licensing. In the niche world of complex system-on-chip (SoC) devices, IP has helped close the infamous design gap with silicon, launch a new industry of fabless companies, and provide a way to meet incredibly short time-to-market (TTM) windows.

Why IP Matters

“As long as new systems companies and fabless semiconductor startups were entering the market, the need for IP increased at a rapid rate,” explains Wally Rhines, an EDA industry veteran, and President/CEO at Cornami, Inc. “As we enter a period of softness in the growth of demand for semiconductors, the rate of that IP demand growth may slow, but it’s still a fundamental megatrend of the EDA industry.”

As designs become increasingly complex, integrating 3rd party IP is no longer optional; it is necessary. However, this challenges the IP providers as the quality, security, and safety requirements are much more significant.

“The IP-XACT standard allows consistent IP hand-off through a standardized interface,” stated Lu Dai, Accellera Systems Initiative Chair. “Because IP-XACT is tool independent, consumers can choose the best tools for their project.”

The importance of IP has also begun to extend into newer, emerging markets. With the slowing of Moore’s Law, the chip industry has turned to other ways of achieving performance, power, and area efficiencies. One of those ways is with advanced IP packaging using 3D IC chiplets – or modular dies – to replace single silicon dies with multiple smaller dies that work together in an integrated packaged solution.

Standards bodies like UCIe were established in 2022 to develop an ecosystem that will hopefully turn the promised plug-and-play capabilities of chiplets into a reality.

“There are many challenges for the design industry to address, but hopefully, the hard lessons learned from the formation of the IP industry in the late 1990s will translate to a faster establishment of formal standards for chiplets to help drive 3D IC integration,” notes Joseph Sawicki, Executive Vice President, Integrated Circuits, Electronic Design Automation at Siemens.

IP-XACT Standard Gains Importance

After several years of hard and dedicated work by the Accellera IP-XACT Working Group, the latest version was approved by IEEE Standards Association Board in September of this year. The significant changes were met with interest during a tutorial presentation at the December 2022 DVCon Europe. But what does this mean to the EDA tools industry and chip designers in general?

To answer those questions, Semiconductor Digest sat down with the working group chair and NXP engineer Erwin de Kock (see Figure 1). What follows is a portion of that interview.

John Blyler/Semiconductor Digest: The idea behind IP-XACT is to enable SoC developers to integrate desired processors, memories, interfaces, and other device IPs into their SoC cores with minimal integration pain. How is this accomplished?

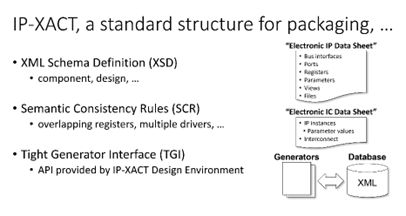

Erwin de Kock/Chair, IP-XACT: IP-XACT is an XML format that defines and describes electronic components and their designs. And that is accomplished by three items (see Figure 2): 1) XML Schema definitions for details, the design, etc.; 2) semantic consistency rules (SCR) for overlapping registers, multiple drives, etc.; and 3) tight generator interfaces (TGI), an API provided by IP-XACT Design Environment.

John Blyler: Is the basic idea that different tools from different vendors can work in the same format by exchanging XML files that adhere to the IEEE-1685-2022 standard?

Erwin de Kock: Yes – and that is why the industry needs the standard. Further, the content of these XML files includes the component schema in a machine-readable format.

Traditionally, designers would exchange a human-readable document in PDF or MS Word format representing the IP data sheet from their IP provider. Then began the arduous task of integrating that IP into their design. Instead of processing that human-readable document, the standard allowed the chip design community to use a machine-readable IP-XACT XML format by loading a file into their preferred tool suite.

John Blyler: Could you continue using your design and verification tools?

Erwin de Kock: Yes, the standard was developed so you could use your tool of choice, and that tool would understand the content of the IP-XACT file. For example, you could include a register description and generate the output you need from that IP register description. Further, you could use a generator from your EDA vendor to create a UVM register model, or you might write your own description and then use the Tight Generator Interface (TGI) that comes with the standard.

John Blyler: Is it possible to add non-standard XML tags in the IP-XACT files to add something unique to your design?

Erwin de Kock: The IP-XACT schema has the notion of vendor extensions, which allow you to add XML content that is not part of the standard. Of course, it is then up to you and your partners to ensure the same interpretation of the content from these vendor extensions. But you can add information in the XML document that is not covered by the standard. In this way, you can add extra things to your flow.

John Blyler: Have vendor extensions grown in popularity?

Erwin de Kock: Accellera first published recommended vendor extensions in the 2009 version of the standard. They covered three areas: analog mix signal, physical design planning, and power. At that time, mixed-signal representations were not covered by the standard, whereas, in the latest 2022 version, mixed-signal ports have become part of the standard – and thus are no longer included as a vendor extension.

Conversely, physical design planning remains a vendor extension since it lacked enough interest to move it into the 2022 standard.

John Blyler: What is an example of a vendor extension?

Erwin de Kock: During DVCon Europe 2022, Arteris provided several examples of how they use vendor extensions to describe hardware access to register fields (see Figure 3).

John Blyler: What precisely are the new features offered by the latest standard?

Erwin de Kock: The new features supported by the changes between IEEE Std. 1685-2014 and IEEE Std. 1685-2022 include:

- Descriptions of HDL structures, unions, and System Verilog interfaces in component ports, as well as design connectivity to support these concepts in netlisting.

- Descriptions of analog and mixed-signal properties in component ports to enable mixed-signal netlisting.

- Descriptions of power domains in components and binding of power domains for component instances. This can be used to detect power domain crossings in the connectivity.

- Descriptions of runtime configurable component model parameters used by runtime configuration mechanisms such as SystemC CCI.

- Descriptions of parameterized register definitions, in addition to register instances, to enable the reuse of such definitions.

- Descriptions of operating modes in components that affect access of incoming and outgoing transactions, access properties of registers and register fields, and memory remapping.

- Description of register field aliasing and broadcasting.

- Support Representational State Transfer Application (REST) as a transport layer for the Tight Generator Interface (TGI)

John Blyler: Can people now look at the 2022 IP-XACT standard?

Erwin de Kock: Accellera has the IEEE Get Program, where you can download a standard for free. This program also serves as a gauge for interest in the standard, as Accellera states that the number of downloads has increased every year. To me, this suggests that IP-XACT remains an essential standard for chip designers and verification engineers.

[Editor’s Note: John Blyler was the technical standard editor for IEEE-1685-2022.]